Results 11,331 to 11,340 of 12091

Thread: Anandtech News

-

10-27-21, 05:03 PM #11331

Anandtech: European Union Regulators Open Probe Into NVIDIA-Arm Acquisition

Following an extended period of regulatory uncertainly regarding NVIDIA’s planned acquisition of Arm, the European Union executive branch, the European Commission, has announced that they have opened up a formal probe into the deal. Citing concerns about competition and the importance of Arm’s IP, the Commission has kicked off a 90 day review process for the merger to determine if those concerns are warranted, and thus whether the merger should be modified or blocked entirely. Given the 90 day window, the Commission has until March 15th of 2022 to publish a decision.

At a high level, the EC’s concerns hinge around the fact that Arm is an IP supplier for both NVIDIA and its competitors. Which has led the EC to be concerned about whether NVIDIA would use its ownership of Arm to limit or otherwise degrade competitors’ access to Arm’s IP. This is seen as an especially concerning scenario given the breadth of device categories that Arm chips are in – everything from toasters to datacenters. As well, the EC will also be examining whether the merger could lead to NVIDIA prioritizing the R&D of IP that NVIDIA makes heavy use of (e.g. datacenter CPUs) to the detriment of other types of IP that are used by other customers.

It is worth noting that this is going to be a slightly different kind of review than usual for the EC. Since NVIDIA and Arm aren’t competitors – something even the EC notes – this isn’t a typical competitive merger. Instead, the investigation is going to be all about the downstream effects of a major supplier also becoming a competitor.

Overall, the need for a review is not terribly surprising. Given the scope of the $40 billion deal, the number of Arm customers (pretty much everyone), and the number of countries involved (pretty much everyone again), there was always a good chance that the deal could be investigated by one or more nations. Still, the EC’s investigation means that, even if approved, the deal will almost certainly not close by March as previously planned.

"Semiconductors are everywhere in products and devices that we use everyday as well as in infrastructure such as datacentres. Whilst Arm and NVIDIA do not directly compete, Arm's IP is an important input in products competing with those of NVIDIA, for example in datacentres, automotive and in Internet of Things. Our analysis shows that the acquisition of Arm by NVIDIA could lead to restricted or degraded access to Arm's IP, with distortive effects in many markets where semiconductors are used. Our investigation aims to ensure that companies active in Europe continue having effective access to the technology that is necessary to produce state-of-the-art semiconductor products at competitive prices."

-Executive Vice-President Margrethe Vestager

More...

-

10-27-21, 05:03 PM #11332

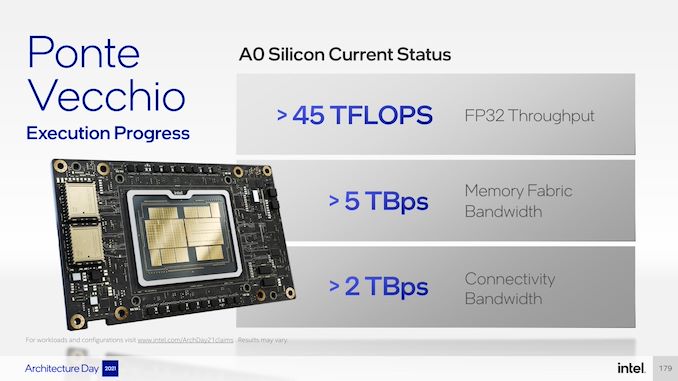

Anandtech: Intel's Aurora Supercomputer Now Expected to Exceed 2 ExaFLOPS Performance

As part of Intel’s 2021 Innovation event, the company offered a brief update on the Aurora supercomputer, which Intel is building for Argonne National Laboratory. The first of the US’s two under-construction exascale supercomputers, Aurora and its critical processors are finally coming together, allowing Intel to finally narrow its performance projections. As it turns out, the 1-and-change exaFLOPS system is going to be more like a 2 exaFLOPS system – Aurora’s performance is coming in high enough that Intel now expects the system to exceed 2 exaFLOPS of double precision compute performance.

Planned to be the first of the US’s two public exascale systems, the Aurora supercomputer has been through a tumultuous development process. The contract was initially awarded to Intel and Cray back in 2015 for a pre-exascale system based on Intel’s Xeon Phi accelerators, a plan that went out the window when Intel discontinued Xeon Phi development. In its place, the Aurora contract was renegotiated to become an exascale system based on a combination of Intel’s Xeon CPUs and what became their Ponte Vecchio Xe-HPC GPUs. Since then, Intel has been working down to the wire on getting the necessary silicon built in order to make a delivery window that’s already shifted from 2020 to 2021 to 2022(ish), going as far as fabbing parts of Ponte Vecchio on rival TSMC’s 5nm process.

But there is finally light at the end of the tunnel, it would seem. As Intel pushes to complete the system, its performance is coming in ahead of expectations. According to the chip company, they now expect that the assembled supercomputer will be able to deliver over 2 exaFLOPS of double precision (FP64) performance. The system previously didn’t have a specific performance figure attached to it, beyond the fact that it would be over 1 exaFLOPS in FP64 throughput.

This higher performance figure for Aurora comes courtesy of Ponte Vecchio, which according to CEO Pat Gelsinger is overdelivering on performance. Gelsinger hasn’t gone into additional detail in how Ponte Vecchio is overdelivering, but given that IPC and overall efficiency tends to be relatively easy to nail down during simulations, the most likely candidate here is that Ponte Vecchio’s is clocking higher than Intel’s previous projections. Ponte Vecchio is one of the first HPC chips (and the first Intel GPU) built on TSMC’s N5 process, so there have been a lot of unknowns going into this project.

For Intel, this is no doubt a welcome bit of good luck for a project that has seen many hurdles. The repeated delays have already allowed rival AMD to get the honors of delivering the first exascale system with Frontier, which is currently being installed and is expected to offer 1.5 exaFLOPS in performance. So while Intel no longer gets to be first, once Aurora does come online next year, it will be the faster of the two systems.

More...

-

10-29-21, 09:37 AM #11333

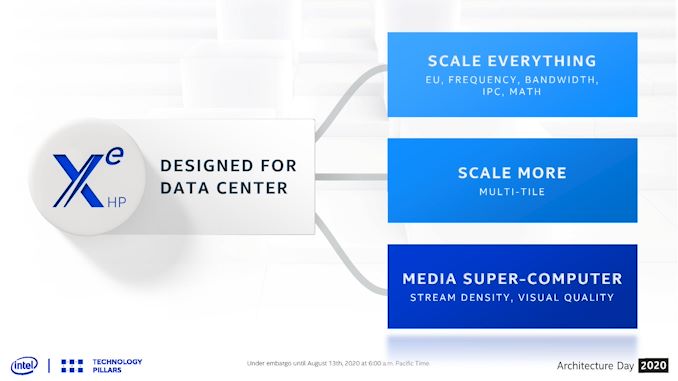

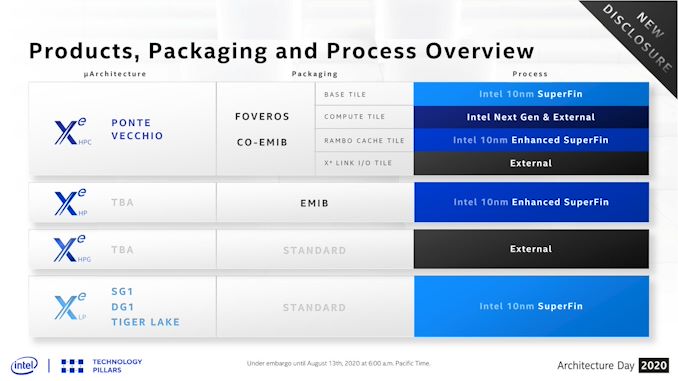

Anandtech: Intel Cans Xe-HP Server GPU Products, Shifts Focus To Xe-HPC and Xe-HPG

In a tweet published yesterday afternoon by Raja Koduri, Intel’s SVP and GM of the Accelerated Computing Systems and Graphics (AXG) Group, the GPU frontman revealed that Intel has dropped their plans to bring their Xe-HP series of server CPUs to the commercial market. Citing that Xe-HP has evolved into the Xe-HPC (Ponte Vecchio) and Xe-HPG (Intel Arc) families within Intel’s GPU group, the company seemingly no longer sees a need to release a second set of server GPUs – at least, not something based on Xe-HP as we know it.

We deployed Xe HP in our oneAPI devcloud and leveraged it as a SW development vehicle for oneAPI and Aurora. We currently don’t intend to productize Xe HP commercially, it evolved into HPG and HPC that are on general market production pathAlso known by the codename Arctic Sound, Intel’s initial family of server GPUs has been the most visible product under development from Intel’s reborn GPU group. Koduri frequently showed off chips housing the silicon as it was brought-up in Intel’s labs. And, Xe-LP/DG1 excepted, this was the first high-performance Xe silicon that Intel developed. Notably, it was also the only high-performance Xe silicon slated to be manufactured by Intel; Xe-HPC’s compute tiles and Xe-HPG dies are both being built by TSMC.

— Raja Koduri (@Rajaontheedge) October 28, 2021

We haven’t heard much of Xe-HP this year, and in retrospect that was a sign that something was amiss. Still, as of year Intel had been showing off Xe-HP demos with performance as high as 42 TFLOPS of FP32 throughput. And in November the company announced that Xe-HP was sampling to select customers.

But, as it would seem, Xe-HP just isn’t meant to be. For 2021 Intel has been focused on getting Ponte Vecchio assembled for the Aurora supercomputer (and eventually other customers), as well as bringing up the Xe-HPG Alchemist GPU family for Q1 of 2022. According to Koduri, Xe-HP has been leveraged as a development vehicle for Aurora and Intel’s oneAPI – so it hasn’t gone unused – but that’s as far as Xe-HP has made it.

For now, the cancellation of Xe-HP raises some big questions about Intel’s server GPU plans. Xe-HP was intended to be the backbone of their server efforts, utilizing a scalable design that could range from one to four cores to serve datacenter needs ranging from compute to media processing. Between Xe-HP and Ponte Vecchio covering the very high end of the market (e.g. HPC), Intel was slated to develop a potent slate of parallel processors to compete with market-leader NVIDIA, and offer traditional Intel customers a GPU option that let them stay in Intel’s ecosystem.

At this point it’s not clear what will fill the void left by Xe-HP in Intel’s product stack. Ponte Vecchio is in production now, and judging from Intel’s revised Aurora figures, is performing better than expected. But the massive chip is expensive to build – at least in its current configuration. And while Xe-HPG could be called up for server use next year, unless Intel is able to tile it like Xe-HP, they won’t be able to offer the kind of performance that Xe-HP was slated to deliver.

Equally nebulous is a full understanding of why Intel opted to cancel Xe-HP. With the silicon already up and running, canceling it certainly sets back their server GPU plans. But as AMD has already begun rolling out their new CDNA2 architecture-based server GPU products, and NVIDIA is likely aiming for some kind of refresh of their own in 2022, there’s certainly the question of whether Xe-HP was simply too late and/or too slow to compete in the server market. Coupled with that, it’s the only lineup of high-performance Xe parts that Intel was fabbing themselves, using the 10nm Enhanced Superfin process (now referred to as Intel 7).

In any case, Intel is clearly not giving up on their plans to break into the server GPU market, even if pieces of that plan now need to be rewritten. We’ve reached out to Intel for additional details, and we’ll update this story further if Intel releases a more detailed statement on their server GPU plans.

More...

-

10-29-21, 09:37 AM #11334

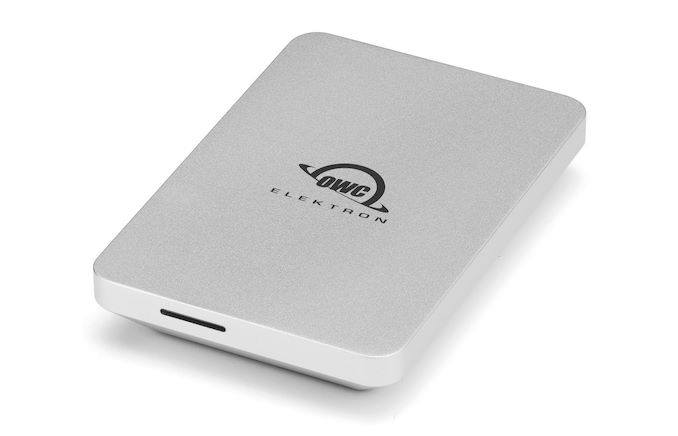

Anandtech: OWC Envoy Pro Elektron Rugged IP67 Portable SSD Review

The market for portable SSDs has expanded significantly over the past few years. With USB 3.2 Gen 2 (10 Gbps) becoming the de-facto standard for USB ports even in entry-level systems, external storage devices using the interface have flooded the market.

OWC has established itself as vendor of computing peripherals and upgrade components (primarily for the Apple market) over the last 30 years. Their portable SSDs lineup, under the Envoy brand, includes both Thunderbolt and USB-C offerings. The Envoy Pro EX Thunderbolt 3 and the Envoy Pro EX USB-C coupled leading performance numbers with a sleek and stylish industrial design. Late last year, the company introduced the OWC Envoy Pro Elektron - a portable flash drive similar to the Envoy Pro EX USB-C in performance, albeit in a much smaller form-factor.

Read on for our hands-on review of the Envoy Pro Elektron to check out how it fares in our updated test suite for direct-attached storage devices.

More...

-

10-29-21, 04:25 PM #11335

Anandtech: Bringing Geek Back: Q&A with Intel CEO Pat Gelsinger

One of the overriding key themes of Pat Gelsinger’s ten-month tenure at Intel has been the eponymous will to ‘bring geek back’ to the company, implying a return to Intel’s competitive past which relied on the expertise of its engineers to develop market-leading products. During this time, Pat has showcased Intel’s IDM 2.0 strategy, leveraging internal production, external production, and an update to Intel’s foundry offering, making it a cornerstone of Intel’s next decade of growth. The first major launch of this decade happened this week, at Intel’s Innovation event, with the announcement of 12th Gen Core, as well as updates to Intel’s software strategy up and down the company.

After the event, Intel invited several media and an analyst or two onto a group session with CEO Pat, along with CTO Greg Lavender, a recent new CTO hire coming from Pat’s old stomping ground at VMWare. In light of the announcements made at Intel Innovation, as well as the financial quarterly results released just the week prior, and the state of the semiconductor supply globally, everyone had Intel at the forefront of their minds, ready to ask for details on Intel’s plan.

More...

-

11-02-21, 10:05 AM #11336

Anandtech: Google's Tensor inside of Pixel 6, Pixel 6 Pro: A Look into Performance &

Today, we’re giving the Tensor SoC a closer look. This includes trying to document what exactly it’s composed of, showcasing the differences or similarities between other SoCs in the market, and better understanding what kind of IPs Google has integrated into the chip to make it unique and warrant calling it a Google SoC.

More...

-

11-04-21, 10:51 AM #11337

Anandtech: The Intel 12th Gen Core i9-12900K Review: Hybrid Performance brings Hybrid

Today marks the official retail availability of Intel’s 12th Generation Core processors, starting with the overclockable versions this side of the New Year, and the rest in 2022. These new processors are the first widescale launch of a hybrid processor design for mainstream Windows-based desktops using the underlying x86 architecture: Intel has created two types of core, a performance core and an efficiency core, to work together and provide the best of performance and low power in a singular package. This hybrid design and new platform however has a number of rocks in the river to navigate: adapting Windows 10, Windows 11, and all sorts of software to work properly, but also introduction of DDR5 at a time when DDR5 is still not widely available. There are so many potential pitfalls for this product, and we’re testing the flagship Core i9-12900K in a few key areas to see how it tackles them.

More...

-

11-05-21, 06:11 AM #11338

Anandtech: VIA To Offload Parts of x86 Subsidiary Centaur to Intel For $125 Million

As part of their third quarter earnings release, VIA Technologies has announced this morning that the company is entering into an unusual agreement with Intel to offload parts of VIA’s x86 R&D subsidiary, Centaur Technology. Under the terms of the murky deal, Intel will be paying Centaur $125 million to pick up part of the engineering staff – or, as the announcement from VIA more peculiarly puts it “recruit some of Centaur's employees to join Intel,” Despite the hefty 9-digit price tag, the deal makes no mention of Centaur’s business, designs, or patents, nor has an expected closing date been announced.

A subsidiary of VIA since 1999, the Austin-based Centaur is responsible for developing x86 core designs for other parts of VIA, as well as developing their own ancillary IP such as deep learning accelerators. Via Centaur, VIA Technologies is the largely aloof third member of the x86 triumvirate, joining Intel and AMD as the three x86 license holders. Centaur’s designs have never seen widescale adoption to the extent that AMD or Intel’s have, but the company has remained a presence in the x86 market since the 90s, spending the vast majority of that time under VIA.

Centaur’s most recent development was the CNS x86 core, which the company announced in late 2019. Aimed at server-class workloads, the processor design is said to offer Haswell-like general CPU performance, which is combined with AVX-512 support (executed over 2 rounds via a 256-bit SIMD). CNS, in turn, would be combined into a product Centaur called CHA, which added fabric and I/O, as well as an integrated proprietary deep learning accelerator. The first silicon based on CHA was originally expected in the second half of 2020, but at this point we haven’t heard anything (though that’s not unusual for VIA).

As for the deal at hand, VIA’s announcement leaves more questions than answers. The official announcement from VIA comes with very few details other than the price tag and the information that Intel is essentially paying Centaur for the right to try to recruit staff members to join Intel. Despite being the buyer in this deal – and buyers typically being the ones to announce acquisitions – Intel has not said anything about the deal from their end.

We’ve reached out to both Intel and Centaur for more information, but we’re not expecting to hear from them until later this morning given the significant time zone gap between Taiwan and the US. In the meantime, local media reports are equally as puzzling, as language barriers aside, apparently even the local press isn’t being given much in the way of concrete details. None the less, local media such as United Daily News is reporting that the Intel deal is indeed not a wholesale sale of Centaur’s team, and that VIA is retaining the Centaur business. So what Intel is getting out of this that’s worth $125 million is, for the moment, a mystery.

Adding an extra wrinkle to matters, the Centaur website has been partially scrubbed. Active as recently as the end of last week, the site’s contents have been replaced with an “under construction” message. In which case it would seem that, even if VIA is retaining Centaur and its IP, the company no longer has a need for a public face for the group.

Meanwhile, given the overall lack of details, news of the acquisition raises a number of questions about the future of VIA’s x86 efforts, as well as just what Intel is getting out of this. If VIA isn’t selling the Centaur business, then does that mean they’re retaining their x86 license? And if Intel isn’t getting any IP, then what do they need with Centaur’s engineering staff? Does Intel want to make their own take on the CNS x86 core?

Overall, it’s not too surprising to see Intel make a play for the far-flung third member of the x86 ecosystem, especially as the combination of AMD and Arm-based processors is proving to be stiff competition for Intel, dampening the need for a third x86 vendor. Still, this isn’t what we envisioned for Intel buying out Centaur.

As always, we’ll have more details on this bizarre story as they become available.

More...

-

11-08-21, 11:15 AM #11339

Anandtech: AMD Announces Instinct MI200 Accelerator Family: Taking Servers to Exascal

AMD today is formally unveiling their AMD Instinct MI200 family of server accelerators. Based on AMD’s new CDNA 2 architecture, the MI200 family is the capstone AMD’s server GPU plans for the last half-decade. By combing their GPU architectural experience with the latest manufacturing technology from TSMC and home-grown technologies such as their chip-to-chip Infinity Fabric, AMD has put together their most potent server GPUs yet. And with MI200 parts already shipping to the US Department of Energy as part of the Frontier exascale supercomputer contract, AMD is hoping that success will open up new avenues into the server market for the company.

More...

-

11-08-21, 11:15 AM #11340

Anandtech: AMD Gives Details on EPYC Zen4: Genoa and Bergamo, up to 96 and 128 Cores

Since AMD’s relaunch into high-performance x86 processor design, one of the fundamental targets for the company was to be a competitive force in the data center. By having a competitive product that customers could trust, the goal has always been to target what the customer wants, and subsequently grow market share and revenue. Since the launch of 3rd Generation EPYC, AMD is growing its enterprise revenue at a good pace, however questions always turn around to what the roadmap might hold. In the past, AMD has disclosed that its 4th Generation EPYC, known as Genoa, would be coming in 2022 with Zen 4 cores built on TSMC 5nm. Today, AMD is expanding the Zen 4 family with another segment of cloud-optimized processors called Bergamo.

More...

Thread Information

Users Browsing this Thread

There are currently 15 users browsing this thread. (0 members and 15 guests)

Quote

Quote

Bookmarks