Results 9,781 to 9,790 of 12096

Thread: Anandtech News

-

08-16-19, 03:17 PM #9781

Anandtech: Micron: Mass Production of 16 Gb DDR4 & LPDDR4X Chips Using 1z nm Technolo

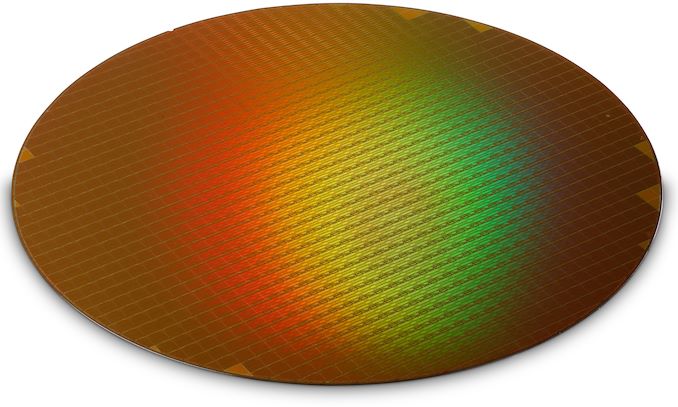

Micron announced on Thursday that it had started volume production of memory chips using its 3rd Generation 10 nm-class fabrication technology (also known as 1Z nm). The first DRAMs to be made using Micron’s 1Z nm process are 16 Gb monolithic DDR4 and LPDDR4X devices, with Micron expected to broaden their portfolio over time.

Micron’s 3rd Generation 10 nm-class (1Z nm) manufacturing process for DRAM will allow the company to increase the bit density, enhance the performance, and the lower power consumption of its DRAM chips as compared to its 2nd Generation 10 nm-class (1Y nm) technology. In particular, the company says that its 16 Gb DDR4 device consumes 40% less power than two 8 Gb DDR4 DRAMs (presumably at the same clocks). Meanwhile, Micron’s 16 Gb LPDDR4X ICs will bring an up to 10% power saving. Because of the higher bit density that the new 1Z nm technology provides, it will be cheaper for Micron to produce high-capacity (e.g., 16 Gb) memory chips for lower-cost, high-capacity memory sub-systems.

The manufacturer did not disclose the speed bins of its 16 Gb DDR4 DRAMs, but expect Micron to be in the official JEDEC ranges. One of the first products to use the company’s 16 Gb DDR4 devices will be high-capacity (e.g., 32 GB and higher) memory modules for desktops, notebooks, and workstations.

As for mobile memory, Micron’s 16 Gb LPDDR4X chips are rated for transfer rates up to 4266 MT/s. Furthermore, along with offering LPDDR4X DRAM packages with up to 16 GB (8x16Gb) of LPDDR4X for high-end smartphones, Micron will offer UFS-based multichip packages (uMCP4) that integrate NAND for storage and DRAM. The company’s uMCP4 family of products aimed at mainstream handsets will include offerings ranging from 64GB+3GB to 256GB+8GB (NAND+DRAM).

Micron did not disclose where it's producing its monolithic 16 Gb DDR4 and LPDDR4X chips using its 1Z nm technology. Typically, the company kicks off volume production using its latest fabrication processes at its plant in Hiroshima, Japan. Meanwhile, there's also been some speculation among analysts that the company is looking forward to running 1Z production lines this year at its Micron Memory Taiwan (former Rexchip Semiconductor) fab near Taichung, Taiwan.

Related Reading:

- Micron’s DRAM Update: More Capacity, Four More 10nm-Class Nodes, EUV, 64 GB DIMMs

- Micron Kicks Off Mass Production of 12 Gb LPDDR4X DRAM Chips

- Crucial 32 GB DDR4 Modules Found in an ASRock System

- ADATA Demonstrates 32 GB DDR4 Modules, Built on Micron 16 Gb

Source: Micron

More...

-

08-16-19, 05:50 PM #9782

Anandtech: Microns Fab 10 Expansion Completed: 96-Layer 3D NAND Production Starts in

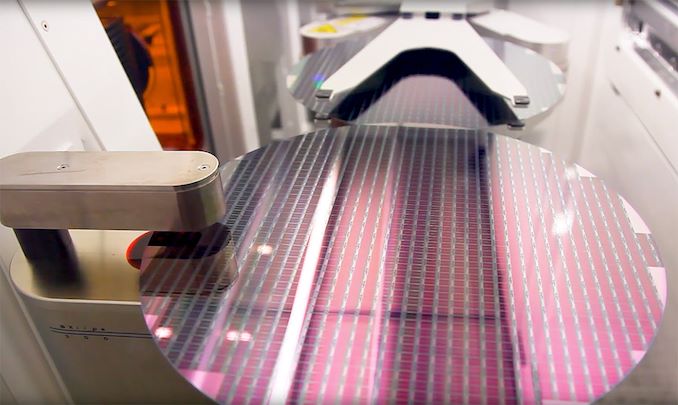

Micron this week hosted a grand opening ceremony of its Fab 10 Expansion in Singapore. The new cleanroom is not expected to increase the company’s production capacity in terms of wafer starts per month, but will enable Micron to continue adopting more advanced 3D NAND process technologies with a higher number of layers and bit density.

The new Fab 10 Expansion is an integral part of Micron’s Fab 10 complex that was previously comprised of Fab 10N and Fab 10X. Officially, it's known that the new 3D NAND production facility is built on a 165,000 m2 land plot, however Micron is not disclosing much else about the usable cleanroom space or other features of the expansion.

Micron is now installing equipment and expects to start production of 96-layer 3D NAND at the new Fab 10 Expansion sometime in the second half of this calendar year (i.e. in the next 4.5 months). Meanwhile, the company stresses that it will align its spending on production tools with 3D NAND demand and trends. Furthermore, even when fully equipped, the facility is not expected to add any new wafer capacity, but rather will be used to house more advanced process equipment necessary for greater numbers of 3D NAND layers.

As the number of 3D NAND layers increases, each wafer has to spend more time inside chemical vapor deposition (CVD) machines, meaning it takes longer to etch them. Adding more time still, various extravagant production techniques like string stacking lengthen manufacturing require even more steps. In order to keep the number of wafers processed consistent as the number of 3D NAND layers grows, flash memory producers have to add extra CVD and etching machines to cleanrooms, which requires extra space. As a result, while bigger fabs may not increase the number of wafer starts per month, they do enable growth in terms of produced NAND flash bits.

Along with the new manufacturing plant, Micron is also expanding its R&D operations in Singapore. Micron’s NAND Center of Excellence will among other things perform technology development and product engineering. Considering how close these functions will be to the actual production facility, the company certainly hopes to improve its yields and productivity at Fab 10.

Related Reading:

- Micron to Expand Its Fab 6 in Virginia, Build New R&D Center

- Micron Starts Construction of Its Third NAND Fab in Singapore

- Intel and Micron To Dissolve 3D XPoint Partnership After 2019

- Intel And Micron To Discontinue Flash Memory Partnership

- Micron Hires New CEO: Sanjay Mehrotra, SanDisk Co-Founder And Former CEO

Sources: Micron, The Strait Times

More...

-

-

08-19-19, 03:15 PM #9784

Anandtech: Hot Chips 31 Keynote Day 1: Dr. Lisa Su, CEO of AMD Live Blog (1:45pm PT)

The keynote for day one at Hot Chips is from Dr. Lisa Su, AMD of CEO. AMD is riding high after successful Ryzen 3000 and 2nd Gen EPYC Rome launches, so it will be interesting to hear what she has to say. Come back at 1:45pm PT (3:45pm ET) to read our live blog.

More...

-

08-19-19, 03:15 PM #9785

Anandtech: Hot Chips 31 Analysis: In-Memory Processing by UPMEM

One of the key critical future elements about this world of compute is moving data about. Moving data requires power, to the point where calling data from memory can consume more power than actually doing ‘compute’ work on it. This is why we have caches, but even these require extensive management built in to the CPU. For simple operations, like bit-shifts or AND operations, the goal is to move the ability to do that compute onto the main DRAM itself, so it doesn’t have to shuttle back and forth. This year at Hot Chips, UPMEM is one of the first companies to showcase their new technology.

More...

-

-

-

-

-

Thread Information

Users Browsing this Thread

There are currently 37 users browsing this thread. (0 members and 37 guests)

Quote

Quote

Bookmarks